## Design and Analysis Of 32 Bit Alu Using Reversible Gates

<sup>1</sup>B. Karunakar, <sup>2</sup>C. Akhil, <sup>3</sup>V. Radhika, <sup>4</sup>I. Nagesh

<sup>1</sup>Assistant professor, karunakar.b@sreenidhi.edu.in, Department of ECE, Sreenidhi Institute Of science and Technology, Hyd

<sup>2,3,4</sup>B.Tech Students, 22315a0430@sreenidni.edu.in, 22315a0432@sreenidhi.edu.in, 22315a0435@sreenidhi.edu.in Department of ECE, Sreenidhi Institute Of science and Technology, Hyd

#### ABSTRACT:

Research into low-power arithmetic logic unit (ALU) designs has been prompted by the growing need for computing that uses less energy. According to Landauer's principle, reversible computing provides a promising solution by reducing information loss and energy dissipation. In this paper, a 32-bit ALU with high computational efficiency and consumption is designed using reversible logic gates. Optimized reversible gate structures, including the Fredkin, Toffoli, Peres, and HNG gates, are used in the implementation of the suggested ALU architecture to carry out arithmetic and logical operations with the least amount of power consumption. Reversible full adders and multiplexers are effectively integrated into the design to carry out basic ALU operations while guaranteeing garbage output and ancilla bit minimization. The power consumption, delay, quantum cost, and hardware complexity of the suggested ALU are assessed.

Key words: Landauers's principle, reversible gates, quantum cost, Fredkin, Toffoli, Peres, HNG gates

## 1- INTRODUCTION

The rapid proliferation of digital systems, particularly in computing and embedded platforms, has raised a growing concern for consumption, heat dissipation, efficiency. Traditional logic gates inherently lose information during computation, which results in energy loss as heat through the paradigm established

by Landauer's principle, which states that energy is dissipated as heat for every bit of information lost (to be at least kT ln2 joules). As device scaling approaches physical limits, minimizing power has been one of the foremost design issues. Reversible computing is a possible approach to address this as it allows us to compute without erasing information and theoretically results in zero energy loss. Constructing a 32-bit Arithmetic Logic Unit (ALU) with reversible logic gates is a significant step toward the realization of low-power, high-efficiency processors for future applications in quantum computing, nanotechnology, and low-power VLSI systems. A reversible 32-bit ALU will not only establish that complex arithmetic and logical operations can be executed using reversible logic but it will also be a baseline for discussing the trade-offs in area, delay, and performance for reversible logic versus traditional irreversible designs. This design can serve as a foundation for developing fully reversible, energy-efficient, and scalable computing architectures.

## 2-LITERATURE REVIEW

1. The authors N. Lathangi and K. B. Ramesh have published a paper titled "Review on Design and Analysis of ALU Using Reversible Logic Gates" in the They cover the use of reversible logic in the design of ALUs in a way that aims to minimize the power consumed in the digital circuits of ALUs. The authors highlight the importance of reversible gates (Feynman, Peres, Toffoli and Fredkin) to minimize power dissipation,

which is particularly important for portable or battery powered devices. The authors discuss different designs for the components of ALUs with reversible logic and evaluates the designs on their ability to optimize power consumption. In conclusion, the authors note that reversible logic design in an ALU reduces the power used, while improving performance, which represents a good opportunity for future energy efficient digital systems.

2. Naman Sharma, Rajat Sachdeva, Upanshu Saraswat, Rajat Yadav, and Gunjeet Kaur present a paper called "Power Efficient Arithmetic Logic Unit Design using Reversible Logic". In their paper, the authors propose a design for an ATU using reversible logic gates in order to improve energy efficiency in digital circuits. The authors acknowledge that reversible logic can greatly minimize the power dissipation during computations, which is especially important in the area of low-power designs, as well as designs applicable to microscopic devices. The intent was to use reversible gates in designing the ALU to minimize information loss (and thus less heat) during computations. In the paper, the authors discuss and offer complete analysis of power, delay and overall performance advantages of the proposed ALU over traditional ALUs.

3. In the article "Design of Logic Gates Using Reversible Gates with Reduced Quantum Cost," authors S. Saniya Samrin et al. present designs for basic logic gates using reversible logic to improve energy efficiency in digital circuits. This study concentrates on decreasing quantum cost, which is a measure of a reversible circuit's complexity, by modelling gates such as AND, OR, and XOR using reversible gates such as the Fredkin gate. This use of reversible gates is presented not only for the sake of reversibility's promise for low-power and high-performance computing.

quantum cost reduction but also to reduce power dissipation and loss of information, which is a primary motivation for reversible computing. The authors believe that these designs could serve as building-block components to construct more complex circuits and provide significant contributions to low power computing in the future. 4. In their paper titled "Reversible Logic Gates and Applications - A Low Power Solution to VLSI Chips," the authors thoroughly discuss a variety of reversible logic gates and the metrics that characterize their performance, particularly quantum cost and gate count. They stress the importance of reversible logic for minimizing power dissipation in VLSI circuits, an important step towards the future of low-power computing methods. This paper also discusses possible application areas with some examples, alluding to the applications of some of these gates in quantum technology or nanotechnology. This thorough discussion represents a valuable set of data for researchers and engineers interested in designing more energy efficient VLSI systems.

5. In their article titled "Optimized Reversible Arithmetic and Logic Unit (ALU)," published in the authors Aprameya R S, Bhargavi N S, Karthik S, and Girija S publish a reversible ALU design to address power dissipation an increasingly important issue in modern VLSI design. This study investigates ways of reducing the number of reversible gates, garbage outputs, constant inputs, and cost in quantum cost. The reversible ALU was designed using Verilog HDL, hardware simulation on Xilinx ISE 14.7, and the results were compared to existing inverter based ALUs. The results show improvements in overall efficiency and performance, demonstration

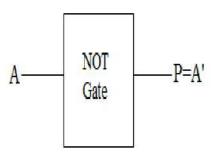

# 3. STUDY OF REVERSIBLE GATES 3.1. NOT GATE

**Description:** The NOT gate is a simple 1x1 reversible gate that has one input and one output ,it simply inverts that input.

Fig 3.1 NOT gate

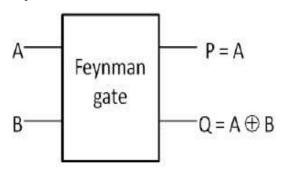

#### 3.2 Feynman Gate (CNOT Gate)

**Description :** The Feynman Gate is a 2x2 reversible gate used in part for duplicating and effectively performs XOR operations

Fig 3.2 Feynman gate

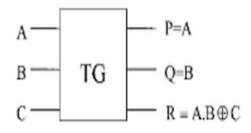

## 3.3 Toffoli Gate:

**Description :** The Toffoli Gate is a simple 3x3 reversible gate designed for universal logic synthesis with the ability to control the inversion of 1 bit associated with 2 control input bits in this gate.

Fig 3.3 Toffoli Gate

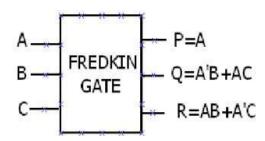

## 3.4 Fredkin Gate

**Description:** It is a reversible 3x3 gate that has a controlled swapping function where one of the inputs (the control) makes the decision to swap or not swap the other two inputs.

Fig 3.4 Fredkin gate

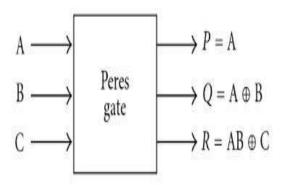

#### 3.5 Peres Gate

**Description:** The Peres Gate is 3x3 reversible gate that executes XOR and AND operations in parallel making it a very effective gate type for arithmetic designs.

Fig 3.5 Peres gate

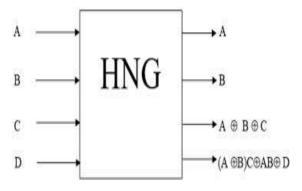

## 3.6 HNG (Haghparast-Navi Gate):

**Description:** The HNG gate is a reversible 4x4 gate for arithmetic applications that produces sum and carry outputs in one step .It is perfect for use in adders.

Fig 3.6 HNG gate

## 4. SCHEMATIC VIEW OF DESIGN

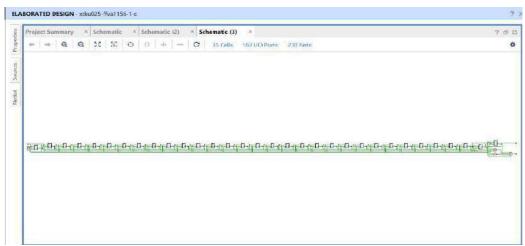

#### 4.1 RTL Schematic of Reversible ALU

Fig 4.1 RTL schematic view of Reversible ALU

In this design, computational units are reused across operations applying control signals to choose the appropriate output to conserve significant gates and interconnects. Because of this logic reuse and tuned selection of reversible gates, the ALU can achieve operation with only 4 functional gate cells running at RTL level. The total net count is controlled to 230

through organized data movement and reduced unnecessary signal propagation and intermediary lines. This efficient design is easily functionally complete and lends itself as ideal for a corresponding low power, reversible logic circuit for quantum computing applications.

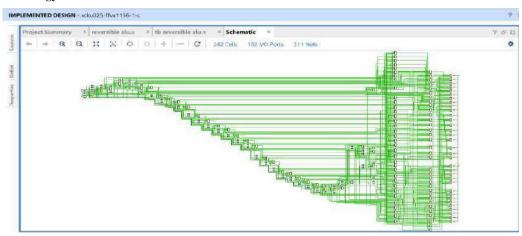

#### 4.2 Technology Schematic of Reversible ALU

Fig 4.2 Technology schematic of reversible ALU

The technology schematic for the 32-bit reversible ALU demonstrates a more detailed and gate-level view of the physical implementation, as it included standard cell mapping post-synthesis. This design

created 311 interconnecting nets and utilizes 242 leaf cells, well-balanced for a reversible logic-based system.

#### 4.3 RTL Schematic of Conventional ALU

Fig 4.3 RTL Schematic of Conventional ALU

The RTL schematic of the traditional 32-bit ALU that uses standard irreversible logic gates has 19 leaf cells and 366 interconnecting nets. This total number of gates and interconnects is more than the reversible ALU design, which had only 4 leaf cells and 230 nets. The use of leaf cells in the traditional design is the result of a separate logic block being used for each

operation, and limited gate reuse or sharing, as is often used in standard ALU designs. Logic that uses irreversible components tends to use greater numbers of interconnects because of fan-out and additional unneeded signal lines, which add power use and area on the die.

#### 4.4 Technology Schematic of Conventional ALU

Fig 4.4 Technology Schematic of Conventional ALU

The technology schematic of the conventional 32-bit ALU indicates that it has 420 nets and 290 leaf cells, illustrating a more complex and hardware-based design when compared to the reversible ALU model (311 nets and 242 leaf cells). The conventional design has a higher gate and net count as it utilized separate logic

blocks, as well as separate handling of fan-out. The reversible ALU design requires less area and power for the same operations through gate reuse and minimized duplication of signals. Overall, the reversible ALU is a more area and power efficient design and will be better suited for low power and quantum applications

## 5. Results and Analysis

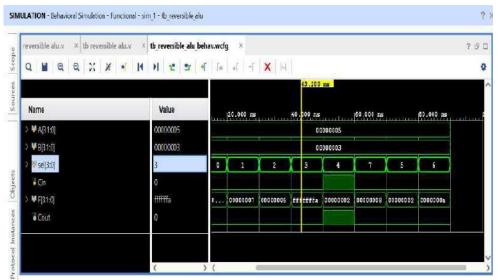

## 5.1 Simulation Result of Reversible ALU

Fig 6.1 simulation result of reversible ALU

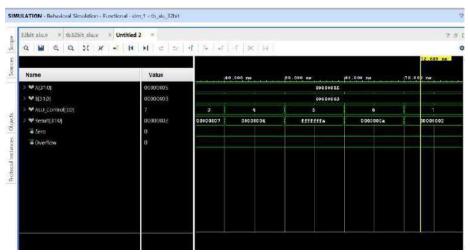

## 5.2 Simulation Results of Conventional ALU

Fig 5.2 Simulation result of conventional ALU

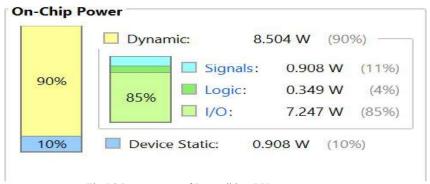

## 5.3 Power report of Reversible ALU

| Power                 | Summary   On-Chip |  |

|-----------------------|-------------------|--|

| Total On-Chip Power:  | 9.141 W           |  |

| Junction Temperature: | 64.1 °C           |  |

Fig 5.3 Power report of Reversible ALU

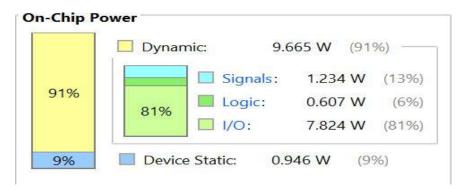

## **5.4 Power Report of Conventional ALU**

| Power                 | Summary   On-Chip      |  |  |

|-----------------------|------------------------|--|--|

| Total On-Chip Power:  | 10.6 <mark>11 W</mark> |  |  |

| Junction Temperature: | 66.4 °C                |  |  |

Fig 5.4 Power report of Conventional ALU

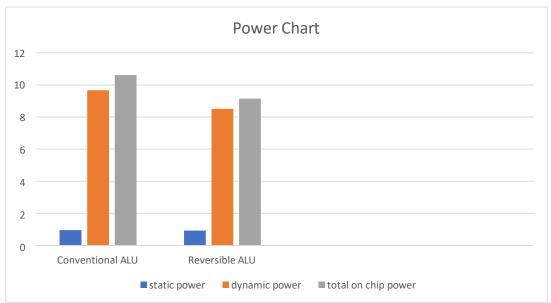

## 5.5 Analysis of power reports;

| S No | Parameter           | Conventional ALU(W) | Reversible ALU(W) |

|------|---------------------|---------------------|-------------------|

| 01   | Static Power        | 0.949               | 0.908             |

| 02   | Dynamic Power       | 9.665               | 8.504             |

| 03   | Total On Chip Power | 10.611              | 9.141             |

Table no 5.5 Comparision of power levels

The power metrics provide clear evidence of the reversible ALU's superior efficiency over the conventional design. The reversible ALU's static power is slightly lower than the conventional ALU's at 0.908 W vs. 0.949 W. This indicates a better level of leakage due to easier logic states and reduced transistor activities in reversible circuits. More importantly, the dynamic power, which mirrors the majority of power used for switching activities, is reduced from 9.665 W in the conventional ALU to 8.504W in the reversible ALU. This reduction of

~12% in dynamic power illustrates the benefit of reversible logic which automatically reduces switching activity and signal fan-out for gate-level designs. Combining these metrics, the total on-chip power consumption of the reversible ALU is 9.141 W compared to 10.611 W with the conventional ALU, representing an overall power reduction of ~13.8%. The reversible ALU is thus a great opportunity for low-power computing in constrained power and/or thermally stressed environments.

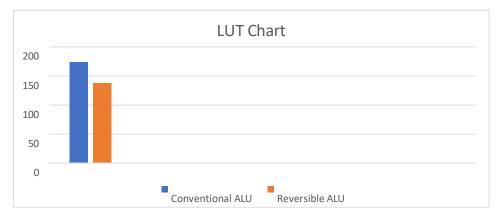

## 5.6 LUT Analysis:

| S No | Conventional ALU | Reversible ALU |

|------|------------------|----------------|

| 01   | 174              | 138            |

Table no 5.6 LUT comparision table

The Look-Up Table (LUT) utilization is an important factor in FPGA-based design as it is a direct reflection of the design's logical complexity and resource efficiency. The results show a reversible ALU design with a logical optimization advantage over the conventional ALU. The conventional ALU had a LUT utilization of 174, while the reversible one used 138, representing a savings of approximately 20.6%. This reduction can be attributed to the advantages of reversible logic gates as Feynman, Peres, and Toffoli gates allow

different combinations of the same logical operations to be performed, without redundancy and rerouting of fan-out feeds. The advantages continue to be demonstrated in the reversible ALU design as proposed in the low-power strategy of working with fewer LUTs confirms an area, power savings, and scalability potential for the intended computing platform, especially for next-generation computing systems being researched for low-power, highdensity computing and quantum computing designs.

#### 5.7 Design Complexity Analysis

| S No | Schematic view | Parameter  | Conventional ALU | Reversible ALU |

|------|----------------|------------|------------------|----------------|

| 01   | RTL Schematic  | Nets       | 366              | 230            |

|      |                | Leaf Cells | 19               | 4              |

| 02   | Technology     | Nets       | 420              | 311            |

|      | Schematic      | Leaf Cells | 290              | 242            |

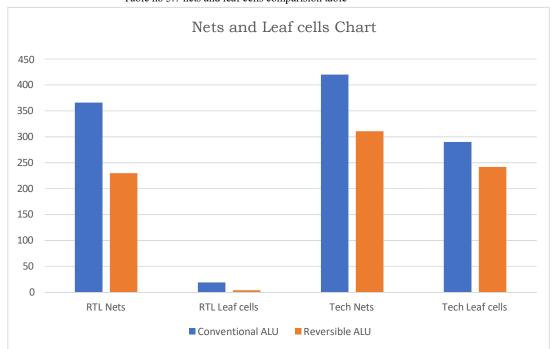

Table no 5.7 nets and leaf cells comparision table

The analysis of the conventional ALU and reversible ALU at the RTL and technology schematic levels demonstrates a clear disparity in design complexity

and utilization of hardware resources .At the RTL schematic level, the conventional ALU utilization included 366 nets and 19 leaf cells, whereas the

reversible ALU used 230 nets and 4 leaf cells. This equates to a 37% reduced number of signal interconnections with the reversible ALU and nearly 79% fewer logic elements when compared to the conventional design. The reduced number of leaf cells in the reversible design is resulting from a

highly optimized logic architecture, in which the reversible gates allow for functional reuse without the necessity for replicated logic, as seen in conventional logic designs. From a technology schematic perspective, which is achieved by synthesizing and mapping each design to actual

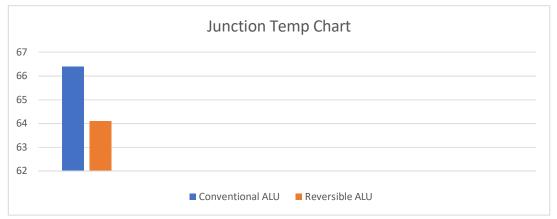

#### 5.8Thermal Analysis:

| S No Conventional ALU |        | Reversible ALU |  |

|-----------------------|--------|----------------|--|

| 01                    | 66.4°C | 64.1°C         |  |

Table no 5.8 comparision of junction temp

The thermal performance of the ALUs was assessed in terms of operating temperature. The conventional ALU operated at 66.4°C, while the reversible ALU operated at 64.1°C. The 2.3°C difference in thermal output demonstrates the reversible ALU's power-efficient and

thermally aware design. Operating at lower temperatures improves the reliability of the system and reduces the need for excessive cooling, making the reversible ALU appropriate for low-power and thermally constrained applications.

## 5.9 Performance Comparision Table

| S no | Parameter           | Conventional ALU | Reversible ALU |

|------|---------------------|------------------|----------------|

| 01   | Static Power        | 0.948 W          | 0.908 W        |

| 02   | Dynamic Power       | 9.605 W          | 8.504 W        |

| 03   | Total On chip power | 10.611 W         | 9.141 W        |

| 04   | RTL Nets            | 366              | 230            |

|      | Tech Nets           | 420              | 311            |

| 05   | RTL Leaf cells      | 19               | 4              |

|      | Tech Leaf cells     | 290              | 242            |

| 06   | LUT                 | 174              | 138            |

| 07   | Junction Temp       | 66.4°C           | 64.1°C         |

Table no 5.9 Performance comparision

## **6.ADVANTAGES & APPLICATIONS**

#### **6.1Advantages:**

A 32-bit ALU is an integral part of any digital asset as it conducts arithmetic and logical operations. Generally speaking, it is found in microprocessors, digital signal processors, and embedded systems. A 32-bit ALU is advantageous when compared to other lower-bit ALUs because it is more capable, faster, and offers more utility.

- 1. Expanded Data Capacity

- 2. Speedier Computation

- 3. Access to Memory efficiency

- 4. Direct support for complex operations

- 5. Diminished Instruction Execution Era

- 6. Power Efficiency

- 7. Scalability Potential for High Performance

## **6.2 Applications:**

- 1. Quantum Computing

- 2. Low-Power Embedded Systems

- 3. Artificial Intelligence and Machine Learning

- 4. Space and Aerospace Systems

- 5. Biomedical Devices:

- 6. Reversible Computing

- 7. Secure and Cryptographic

- 8. Nanotechnology-Based Circuits

- 9. Arithmetic Units in Optical Computing

- 10. Data Centers and Green Computing

- 11. Energy-Harvesting Systems

- 12. Edge and Fog Computing

## 7.CONCLUSION AND FUTURE SCOPE

#### 7.1Conclusion

The differences in characteristics between the conventional ALU and the reversible ALU demonstrate the clear benefits of reversible logic in power consumption, resource utilization, and thermal performance. The reversible ALU provides a 13.85% decrease in total power across all states, including significant reductions in both static and dynamic power, 4.32% and 11.46%, respectively. This overall reduction in power consumption can drive lower energy consumption and improved efficiency. In terms of hardware optimization, the reversible ALU provides

a significant reduction in hardware resources, RTL or technology-level resources, with 78.95% reduction in RTL leaf resources and 20.69% reduction in LUTs. These numbers indicate a more compact and areaefficient design. Additionally, the reversible ALU operates with a lower junction temperature, 64.1°C, to the ALU's 66.4°C, noting a 2.3°C difference contributing to the thermal stability and thermal reliability. Temperature control is imperative for maintaining advanced integrated circuits longevity and safe operation. The reversible ALU also outperforms the conventional ALU from a more holistic view across a number of important parameters, resulting in a very compelling candidate system for applications that are power sensitive thermally constrained or both, in consumer products, such as portable devices, IoT applications and future computing platforms.

## 7.2 Future Scope

The successful implementation and performance of the reversible ALU open a range of possibilities for future directions in digital design. One important direction is to scale reversible logic to more complex architectures such as reversible DSP units, control units, and possibly full-scale reversible processors. progression could eventually lead to fully reversible computing platforms. Further, as reversible logic is closely related to quantum computing principles, this ALU can be the basic building block for hybrid systems already interfacing classical to quantum computing. The reversible ALU also exhibits low power and decreased thermal footprint making it an ideal candidate for integration in energy-limited environments like IoT devices, wearable electronics, and edge computing systems. Research could evaluate more optimization at both gate and architectural levels to improve speed, area, and pipeline compatibility. Additionally, it may be possible to extend reversible logic to reversible memory and interconnect systems both enhancing complete reversible computing systems and reduce energy dissipation and heat.

Another avenue ripe with promise is the infusion

of fault-tolerance techniques into reversible circuits which would be especially applicable in mission-critical situations like the aerospace, medical electronics, or secure computing domains. Finally, the creation of appropriate Electronic Design Automation (EDA) tools and simulation environments specifically for reversible logic will be critical for scalable adoption and industrial deployment. Ultimately, the reversible ALU provides a strong basis for creating energy efficient, thermally-stable, and modal digital systems.

#### 8.REFERENCES

- [1].N.Lathangi, K.B. Ramesh "Review on Design and Analysis on ALU using reversible gates " International journal of Recent Advances in multidisciplinary Topics, volume 3, no 2, 31-34, Feb 2022

- [2]. Naman Sharma, Rajat Sachdeva, Upanshu Saraswat, Rajat Yadav, and Gunjeet Kaur "Power Efficient ALU Design using reversible Logic" International journal of Computer Applications, volume 128, no 6,36-41,Oct 2015

- [3].S.Saniya Samrin, Rachamma patil, Samangala Itagi and others"Design of logic gates using reversible gates with reduced quantum cost"Global Transistion Procedings (2022),136-141

- [4].Kanchan S Tiwari, Rekha S Kadam and others "Reversible Logic gates & Applications-A low power solution to vlsi chips" Mathematical modelling of Engineering problems "Vol 11,no 3,705-720,,march 2024

- [5].Aprameya ,Bhargavi NS, Karthik, Girija "Optimized Reversible ALU"International Journal of Engineering Research & Applications Vol 10,,no 8,,33-38

- [6].K Kiran Kumar, Ajay Kumar "Design of ALU using Reversible logic"International Journal of Technological Research in Engineering Vol 2,,no 3,,162-165 "November 2014

- [7].K.Navya, N. Surya Teja, Sharath Chandra chary "Single Bit ALU using Reversible gates" International

- Research journal of modernization in Engineering Technology & Science "vol 6,,no 2,,1002-1031,,Dec 2024

- [8].Harsh Abhijit Bhaskar "Harsh Sharad Kumar "Review on Reversible Logic gates" International journal for Research in applied Science & Engineering Technology "vol 11,,no 11,,2058-2063,,nov 2023

- [9].G. Jagadeshwar Reddy, "S.Siddeshwar Reddy, "Sujitha "An Area Efficient ALU using Reversible Gates" Internaional Journal of Electrical & Computer Communication Engineering "vol 6,,no 2,,170-175,,nov 2023

- [10].Rangaraju,Akash Babu, Muralidhara "Design and optimization of reversible multiplier circuit" International journal of computer Applications

Vol 52,,no 10 ,,44-50,,Aug 2012